Ana dezavantajı birleşimsel devre mevcut ve önceki durumları kaydetmek için herhangi bir hafıza kullanmaz. Dolayısıyla, önceki giriş durumunun devrenin mevcut durumu üzerinde herhangi bir etkisi yoktur. Oysa sıralı devrenin hafızası vardır, bu nedenle çıktı, girişe göre değişebilir. Bu tür devreler önceki girişi, çıkışı, saati ve bir bellek elemanını kullanır. Burada hafıza öğeleri mandallı veya parmak arası terlikler olabilir. Sıralı devreler, ROM'lar ve çevirmeler, PLA'lar gibi çeşitli yöntemlerle tasarlanmıştır. CPLD'ler (Karmaşık Programlanabilir Mantık Aygıtı) , FPGA'lar (Alan Programlanabilir Kapı Dizisi) . Bu yazıda, sadece PLA'lar kullanılarak sıralı bir devrenin nasıl tasarlanacağını tartışacağız.

Sıralı devrenin blok şeması aşağıda gösterildiği gibi:

Sıralı Devrenin Blok Şeması

PLA'ları Kullanarak Sıralı Devrenin Tasarlanması

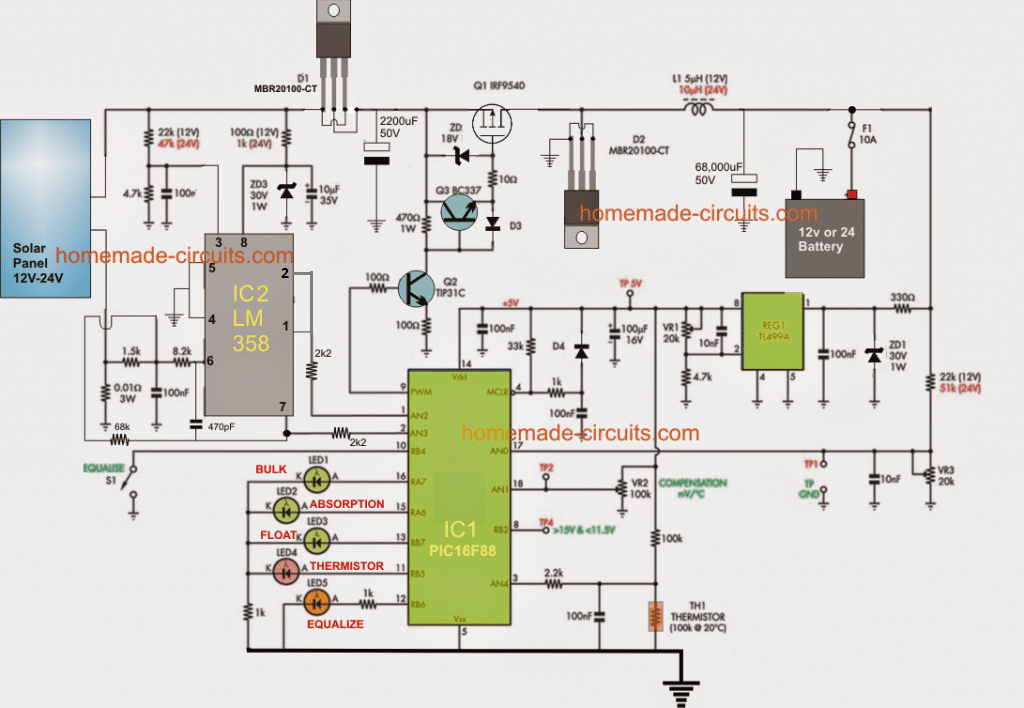

Sıralı devreler PLA'lar (Programmable Logic Arrays) ve flip-floplar kullanılarak gerçekleştirilebilir. Bu tasarımda, durum ataması önemli olabilir, çünkü iyi bir durum atamasının kullanılması gereken ürün terimi sayısını azaltabilir ve dolayısıyla PLA'nın gerekli boyutunu azaltabilir. Her değişmez değerin bir değişken veya olumsuzlama olduğu, değişmez değerlerin birleşimi olarak tanımlanan bir ürün terimi.

Çünkü tasarımı bir kod dönüştürücü olarak ele alalım. Aşağıdaki tabloda gösterilen durum tablosu, bir PLA ve üç parmak arası terlik aşağıdaki şekilde gösterildiği gibi. Bu devre konfigürasyonu, ROM'un uygun boyuttaki PLA ile değiştirilmesinin dışında, ROM flip-flop tabanlı tasarıma çok benzer. Devlet tahsisi, aşağıda verilen doğruluk tablosuna götürür. Bu tablo, dört giriş, 13 ürün terimi ve dört çıkış içeren bir PLA'da saklanabilir, ancak bu, 16 kelimelik ROM ile karşılaştırıldığında boyut olarak biraz küçültülmüş olabilir.

| X Q1 Q2 Q3 | D1 D2 D3 ile |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tablo: Hakikat Tablosu

MEVCUT DURUM

| SONRAKİ DURUM X = 0 1 | MEVCUT ÇIKIŞ (Z) |

| KİME | M.Ö | 1 0 |

B C | D E Ve E | 1 0 0 1 |

D DIR-DİR | H H H M | 0 1 1 0 |

H M | Bir A K - | 0 1 1 - |

Tablo: Durum Tablosu

PLA Kullanarak Ardışık Devrelerin Tasarımı

Karnaugh Haritası Tarafından Türetilen Giriş Çıkış Denklemleri

Burada yedi durum olduğu için üç D parmak arası terlik gereklidir. Bu nedenle 4 girişli ve 4 çıkışlı bir PLA devresi gereklidir. Kod dönüştürücünün durum ataması dikkate alınırsa, ortaya çıkan çıktı denklemi ve Karnaugh'dan türetilen D flip-flop giriş denklemleri aşağıdaki denklemlerle yazılabilir.

D1 = Q1 + = Q2 ”

D2 = S2 + = S2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X S3

| X Q1 Q2 Q3 | D1 D2 D3 ile |

- - 0 - - 1 - - - 1 1 1 0 1-0 100 - 0 - - 0 on bir

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Bu denklemlere karşılık gelen PLA tablosu yukarıdaki tabloda verilmiştir. Bu tablo, dört giriş, yedi ürün terimi ve dört çıkış içeren PLA kullanılarak gerçekleştirilebilir. Yukarıdaki tasarımın işleyişini başlangıçta doğrulamak için, X = 0 ve Q1Q2Q3 = 000 olduğunu varsayın. Bu, tablodaki - - 0- ve 0 - - -0 satırlarını seçer, yani Z = 0 ve D1D2D3 = 100. Etkin saat kenarından sonra, Q1Q2Q3 = 100. Bir sonraki giriş X = 1 ise, o zaman - - 0 - ve - 1- - satırları seçilir, yani Z = 0 ve D1D2D3 = 110. Etkin saat kenarından sonra, Q1Q2Q3 = 110.

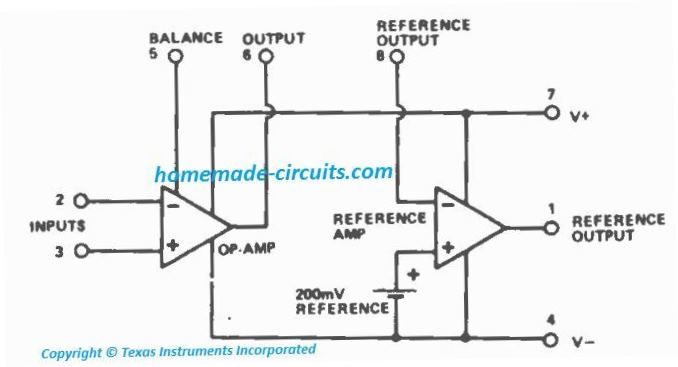

Programlanabilir Mantık Dizisi (PLA)

Programlanabilir Mantık Dizisi, programlanabilir bir mantıksal aygıttır. Genellikle kombinasyonel mantık devrelerini uygulamak için kullanılır. PLA, bir dizi programlanabilir VEYA düzlemine (OR dizisi) bağlanan bir dizi programlanabilir AND düzlemine (AND dizisi) sahiptir ve bu, daha sonra bir çıktı üretmek için geçici olarak tamamlanabilir. Bu düzen, çok sayıda mantık fonksiyonunun içinde sentezlenmesine izin verir. ürünlerin toplamı (SOP) kanonik formlar. Bir PLA'nın basit bir blok diyagramı aşağıda verilmiştir.

Bir PLA'nın Blok Şeması

PLA ve PAL (programlanabilir dizi mantığı) arasındaki temel fark,

PLA: İkisi de VE düzlemi ve OR düzlemi programlanabilir.

PAL: Yalnızca VE düzlemi programlanabilirken OR düzlemi sabittir.

PLA'nın daha iyi anlaşılması için, burada aşağıdaki örneği ele alıyoruz.

Şimdi f1 ve f2 fonksiyonlarını şu şekilde verelim:

X1, x2, x3 girişleri ve bunların tamamlayıcı sinyalleri programlanabilir AND düzlemine verilir, burada AND düzlemi çıkışlarını P1, P2, P3 olarak adlandırılan mintermler olarak alacağız. Daha sonra bu sinyaller, gerekli çıktı fonksiyonu f1 ve f2'yi (ürünlerin toplamı) üretmek için programlanabilir OR düzlemine verilir. Aşağıdaki şekil, belirli işlevsellik için PLA'nın geçit seviyesi uygulamasını açıklamaktadır.

PLA'nın uygulanması

Bu tamamen PLA Kullanarak Sıralı Devrelerin Tasarlanması ile ilgilidir. Bu makalede verilen bilgilerin, bu kavramı daha iyi anlamanıza yardımcı olacağını düşünüyoruz. Ayrıca, bu makaleyle ilgili herhangi bir sorunuz veya elektrik ve elektronik projeleri uygulamak aşağıdaki yorum bölümünde yorum yaparak bize ulaşabilirsiniz. İşte sana bir soru Sıralı bir devre ile ne kastedilmektedir?