Önerilen 4kva'nın bu ilk bölümü senkronize edildi istiflenebilir invertör devresi Frekans, faz ve voltaj açısından önemli otomatik senkronizasyonun 4 invertör arasında nasıl uygulanacağını tartışarak, invertörlerin birbirinden bağımsız olarak çalışmasını ve aynı zamanda birbiriyle eşit bir çıkış elde etmesini sağlar.

Fikir, Bay David tarafından talep edildi. Onunla aramızdaki aşağıdaki e-posta görüşmesi, önerilen Senkronize 4kva İstiflenebilir İnvertör Devresinin ana özelliklerini detaylandırıyor.

E-posta 1

Merhaba Swagatam,

Öncelikle dünyaya genel olarak katkılarınızdan dolayı teşekkür etmek istedim, bilgi ve en önemlisi diğer insanlara yardım etmek için bilgilerinizi paylaşma isteğiniz birçok nedenden ötürü paha biçilemez.

Paylaştığınız devrelerin bazılarını kendi amaçlarıma uyacak şekilde geliştirmek istiyorum, maalesef devrelerde neler olup bittiğini anlarken değişiklikleri kendim yapacak yaratıcılık ve bilgiden yoksunuz.

Devreleri genellikle küçüklerse takip edebilirim ve daha büyük şemalara nerede katıldıklarını / bağlandıklarını görebilirim.

Mümkünse, ne elde etmek istediğimi açıklamaya çalışmak isterim, ancak çok meşgul bir insan olduğunuz ve değerli zamanınızı gereksiz yere kullanmak istemeyeceğiniz konusunda hiçbir yanılsama içinde değilim.

Nihai hedef, Solar PV, Yel Değirmenleri ve biyodizel jeneratörleri kullanarak çok kaynaklı bir yenilenebilir enerji mikro şebekesini inşa etmek (bileşenlerini birleştirmek) olacaktır.

İlk adım, PV güneş invertörü iyileştirmeleridir.

Sabit bir 2kW 230V çıkışı koruyabilen 48 volt saf sinüs dalgalı invertör devrenizi kullanmak istiyorum, çok kısa bir süre için bu çıkışın en az 3 katını verebilmelidir.

Bunu başarmak istediğim temel değişiklik, paralel olarak çalışmak ve bir AC baraya bağlanmak için bu invertör ünitelerinin bir kısmını oluşturmaktır.

Her bir invertörün, AC barasını frekans, gerilim ve akım (yük) için bağımsız ve sürekli olarak örneklemesini istiyorum.

Bu invertörlere köle birimleri diyeceğim.

Ters çevirme modülleri fikri 'tak ve çalıştır' olacaktır.

İnverter, AC bara çubuğuna bağlandıktan sonra sürekli olarak AC bara çubuğundaki frekansı örnekleyecek / ölçecek ve bu bilgiyi, bir 4047 IC girişini sürmek için kullanacak, böylece saat çıkışı, frekansı tam olarak klonlayana kadar ilerletilebilir veya geciktirilebilir. AC bara iki dalga formu senkronize olduğunda, invertör, invertör çıkış aşamasını AC bara çubuğuna bağlayan bir kontaktörü veya röleyi kapatacaktır.

Çubuktaki frekansın veya voltajın önceden belirlenmiş bir toleransın dışına çıkması durumunda, evirici modülü, kendi kendini korumak için sürücü çıkış aşamasını AC çubuğundan etkin bir şekilde ayırarak çıkış aşamasındaki röleyi veya kontaktörü açmalıdır.

Ek olarak, AC baraya bağlandıktan sonra, bağımlı üniteler uykuya geçer veya en azından invertörün çıkış aşaması, çubuk üzerindeki yük tüm bağımlı inverterlerin toplamından daha az iken uyur. AC baraya bağlı 3 bağımlı eviricinin olacağını, ancak çubuğun üzerindeki yük sadece 1,8kW ise diğer iki bağlayıcının uykuya dalacağını hayal edin.

Karşılık, eğer çubuk üzerindeki yük 3kW demek için sıçrarsa, uyuyan terslerden biri, ilave olarak gerekli enerjiyi sağlamak için anında uyanır (zaten senkronize olur).

Her bir çıkış aşamasındaki bazı büyük kapasitörlerin gerekli enerjiyi sağlayacağını ve invertör uyanırken çok kısa bir ana sahip olacağını hayal ediyorum.

Her bir invertörü doğrudan birbirine bağlamamak, aksine bağımsız olarak otonom olmaları tercih edilir (sadece bence).

Mikro denetleyicilerin veya birimlerin hatalarını veya birbirlerini veya sistemde 'adresleri' olan birimleri denetlemekten kaçınmaya çalışmak istiyorum.

Aklımın gözünde, AC bara üzerine ilk bağlanan cihazın sürekli bağlı olan çok kararlı bir referans invertörü olacağını hayal ediyorum.

Bu referans invertör, diğer bağımlı birimlerin kendi ilgili çıkışlarını oluşturmak için kullanacakları frekans ve voltajı sağlayacaktır.

Maalesef, bağımlı birimlerin her birinin potansiyel olarak referans birim haline geleceği bir geri bildirim döngüsünü nasıl önleyebileceğiniz konusunda kafa yoramıyorum.

Bu e-postanın kapsamının ötesinde, yükün maksimum DC çıkış kapasitesini aşması durumunda enerji sağlamak için referans invertöre senkronize olan AC barasına bağlanmak istediğim bazı küçük jeneratörlerim var.

Genel öncül, AC baraya sunulan yükün, kaç tane invertörün ve nihayetinde kaç jeneratörün talebi karşılamak için otonom olarak bağlanacağını veya bağlantısını keseceğini belirleyeceğidir, çünkü bu, umarız enerji tasarrufu sağlar veya en azından enerji israf etmez.

Tamamen birden fazla modülden inşa edilen sistem, daha sonra genişletilebilir / daraltılabilir ve aynı zamanda sağlam / esnek olacaktır, öyle ki herhangi biri veya belki iki ünite arızalanırsa, sistem düşük kapasitede de olsa çalışmaya devam eder.

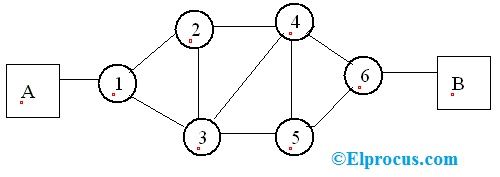

Bir blok diyagram ekledim ve şimdilik pil şarjını hariç tuttum.

Batarya bankasını AC veriyolundan şarj etmeyi ve bu şekilde 48V DC'ye düşürmeyi planlıyorum, bu şekilde jeneratörlerden veya yenilenebilir enerji kaynaklarından şarj edebilirim, bunun belki de DC mppt kullanmak kadar verimli olmadığını biliyorum ama düşünüyorum da verimlilikte kayıp esneklik kazanıyorum. Kasabadan veya elektrik şebekesinden çok uzakta yaşıyorum.

Referans için AC bara üzerinde 2kW'lık bir minimum sabit yük olacaktır, ancak tepe yük 30kW kadar artabilir.

Planım, güneş PV panelleri ve iki 3kW (tepe) yel değirmeni tarafından sağlanacak olan ilk 10 ila 15kW için yel değirmenleri, DC'ye AC doğrultulmuş vahşi ve 1000Ah 48 voltluk bir akü bankası. (Pil ömrünü uzatmak için kapasitesinin% 30'undan fazlasını boşaltmaktan / boşaltmaktan kaçınmak istediğim), kalan seyrek ve çok kesintili enerji talebi, jeneratörlerim tarafından karşılanacaktır.

Bu seyrek ve aralıklı yük atölyemden geliyor.

Hava kompresörüm ve masa testeremdeki motor gibi herhangi bir endüktif yük başlatma akımının sistem boşluğunu işlemek veya almak için bir kapasitör bankı inşa etmenin akıllıca olabileceğini düşünüyordum.

Ancak şu anda daha iyi / daha ucuz bir yol olup olmadığından emin değilim.

Düşünceleriniz ve yorumlarınız çok takdir edilecek ve değer verilecektir Umarım bana geri dönmek için zamanınız olur.

Zamanınız ve ilginiz için şimdiden teşekkür ederim.

Saygılarımızla David, BlackBerry® kablosuz cihazımdan gönderildi

Cevabım

Merhaba David,

İhtiyacınızı okudum ve umarım doğru anladım.

4 invertörden yalnızca biri kendi frekans jeneratörüne sahip olurken, diğerleri bu ana invertör çıkışından frekansı çıkararak çalışır ve bu nedenle hepsi birbiriyle ve bu ana invertörün özellikleriyle senkronize olur.

Onu tasarlamaya çalışacağım ve umduğum gibi ve belirttiğiniz özelliklere göre çalışmasını umacağım, ancak uygulamanın, kavramı anlayabilen ve nerede olursa olsun onu mükemmel hale getirebilen / değiştirebilen bir uzman tarafından yapılması gerekecektir. gereklidir .... aksi takdirde bu oldukça karmaşık tasarımla başarılı olmak son derece zor hale gelebilir.

Sadece temel konsepti ve şemayı sunabilirim .... dinlenme sizin tarafınızdan mühendisler tarafından yapılacaktır.

Tamamlamam biraz zaman alabilir, çünkü Kuyrukta zaten bekleyen çok sayıda isteğim var ... Gönderildiği gibi sizi oğlum olarak bilgilendireceğim

Saygılarımızla Swag

E-posta 2

Merhaba Swagatam,

Çok hızlı yanıtınız için çok teşekkür ederim.

Aklımdaki tam olarak bu değildi ama kesinlikle bir alternatifi temsil ediyor.

Benim düşüncem, her bir birimin biri AC bara üzerindeki frekansa bakan iki frekans ölçüm alt devresine sahip olacağı ve bu birimin invertör sinüs dalgası üreteci için saat darbesini oluşturmasıydı.

Diğer frekans ölçüm alt devresi, inverter sinüs dalgası üretecinin çıkışına bakacaktır.

Saat sinyalini ilerletmek veya sinüs dalgası üretecinden gelen çıktı AC çubuğundaki sinüs dalgasıyla tam olarak eşleşene kadar saat sinyalini geciktirmek için invertör sinüs dalgası üreteci saat darbesine geri beslenen bir opamp dizisi kullanan bir karşılaştırma devresi olabilirdi. .

Eviricinin çıkış aşamasının frekansı AC barasının frekansı ile eşleştiğinde, eviricinin çıkış aşamasını tercihen sıfır geçiş noktasında AC çubuğuna bağlamayı kapatacak bir SSR olacaktır.

Bu şekilde herhangi bir invertör modülü arızalanabilir ve sistem çalışmaya devam edebilir. Ana eviricinin amacı, tüm evirici modüllerinin asla uyumayacağı ve ilk AC bar frekansını sağlayacağıydı. ancak başarısız olursa, diğer birimler 'çevrimiçi' olduğu sürece etkilenmeyecektir.

Yük değiştikçe bağımlı birimler kapanmalı veya başlatılmalıdır.

Gözlemleriniz doğruydu Ben bir 'elektronik' adam değilim, bir makine ve elektrik mühendisiyim Soğutucular, jeneratörler ve kompresörler gibi büyük tesis parçalarıyla çalışıyorum.

Bu proje ilerledikçe ve daha somut hale gelmeye başladığında, bir para hediyesini kabul etmek ister misiniz? Çok şeyim yok, ancak web sitenizin barındırma maliyetlerini desteklemeye yardımcı olmak için paypal yoluyla biraz para hediye edebilirim.

Tekrar teşekkürler.

Cevabınızı sabırsızlıkla bekliyorum.

Namaste

David

Cevabım

Teşekkürler David,

Temel olarak, inverterlerin frekans ve faz açısından birbirleriyle senkronize olmasını ve ayrıca her birinin ana invertör olma ve herhangi bir nedenle bir önceki invertör arızalanması durumunda yükü devralma kabiliyetine sahip olmasını istersiniz. Sağ?

Karmaşık IC'leri veya konfigürasyonları kullanarak değil, sahip olduğum bilgiyle ve biraz sağduyu ile bunu düzeltmeye çalışacağım.

Saygılarımızla Swag

E-posta 3

Merhaba Swag,

Bu, bir ek gereksinimi dikkate alarak bir somun kabuğunda.

Yük düştüğünde, İnvertörler eko veya bekleme moduna geçer ve yük arttıkça veya arttıkça, talebi karşılamak için uyanırlar.

Gideceğin yaklaşımı seviyorum ...

Çok teşekkür ederim, bana olan ilginiz çok takdir ediliyor.

Namaste

Saygılarla

David

Dizayn

Bay David'in talep ettiği gibi, önerilen 4kva istiflenebilir güç çevirici devrelerinin, bağlı olana doğru miktarda kendi kendini düzenleyen güç sağlamak için birbiriyle uygun şekilde eşzamanlı olarak istiflenebilen 4 ayrı evirici devresi şeklinde olması gerekir. Bu yüklerin nasıl AÇIK ve KAPALI olduğuna bağlı olarak yükler.

GÜNCELLEME:

Biraz düşündükten sonra, tasarımın aslında çok karmaşık olması gerekmediğini, bunun yerine aşağıda gösterildiği gibi basit bir konsept kullanılarak uygulanabileceğini fark ettim.

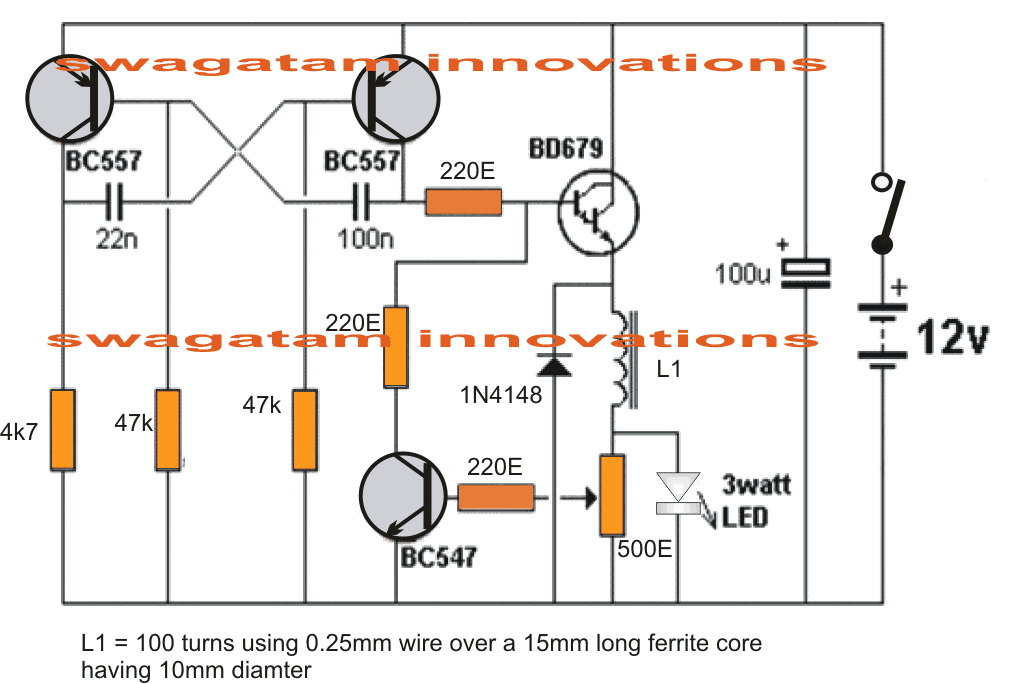

Gerekli sayıda invertör için yalnızca ilişkili diyotları, transistörleri ve transformatör ile birlikte IC 4017'nin tekrarlanması gerekecektir.

Osilatör tek parça olacaktır ve pin3'ü IC 4017'nin pimi14 ile entegre edilerek tüm eviricilerle paylaşılabilir.

Geri besleme devresi, tüm eviriciler için kesme aralığının tam olarak eşleşmesi için, her bir eviriciye tam olarak ayarlanmalıdır.

Yukarıda çok daha kolay bir versiyon güncellendiği için aşağıdaki tasarımlar ve açıklamalar göz ardı edilebilir.

İnvertörleri Senkronize Etme

Buradaki temel zorluk, ana inverter çalışır durumda olduğu ve bir durumda (olası olmasa da) ana inverter arızalanır veya çalışmayı durdurursa, her bir bağımlı inverterin master inverter ile senkronize olmasını sağlamaktır, sonraki inverter şarj eder ve ana inverterin kendisi olur.

İkinci inveterin de başarısız olması durumunda, üçüncü invertör komutu alır ve ana invertör rolünü oynar.

Aslında, eviricilerin senkronizasyonu zor değildir. SG3525, TL494 vb. IC'ler kullanılarak kolayca yapılabileceğini biliyoruz. Bununla birlikte, tasarımın zor kısmı, ana invertör arızalanırsa, diğer invertörlerden birinin hızlı bir şekilde master haline gelmesini sağlamaktır.

Ve bunun, bir saniye için bile frekans, faz ve PWM üzerindeki kontrolü kaybetmeden ve yumuşak bir geçişle gerçekleştirilmesi gerekir.

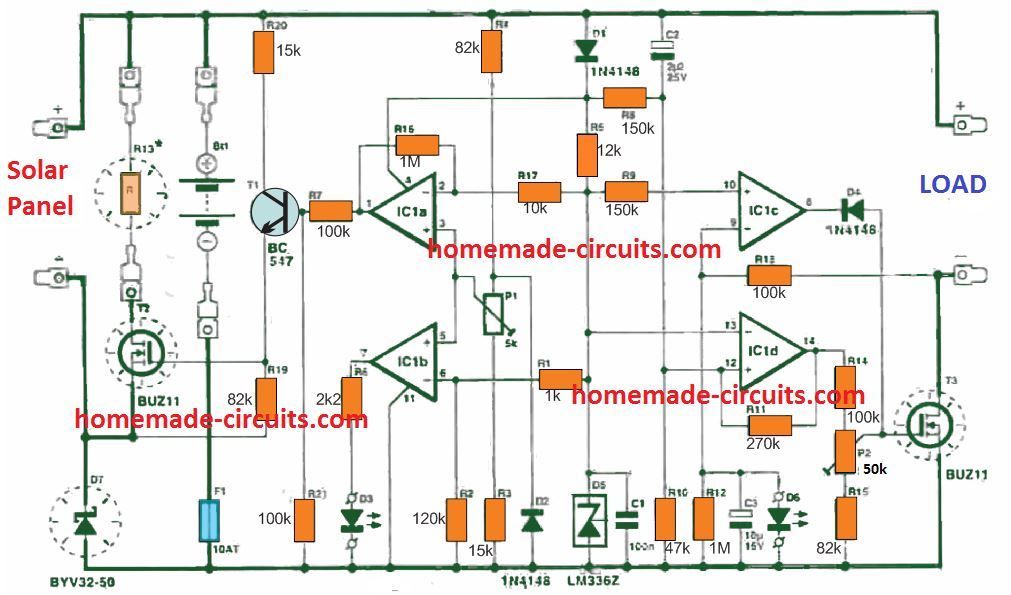

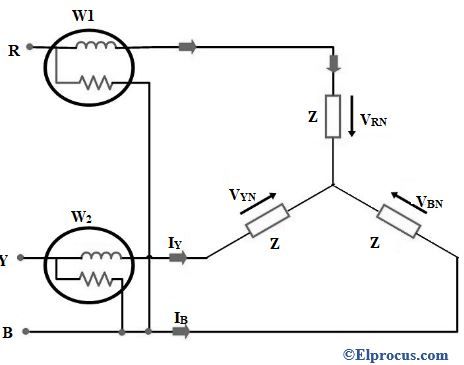

Çok daha iyi fikirlerin olabileceğini biliyorum, bahsedilen kriterleri yerine getirmek için en temel tasarım aşağıdaki diyagramda gösterilmektedir:

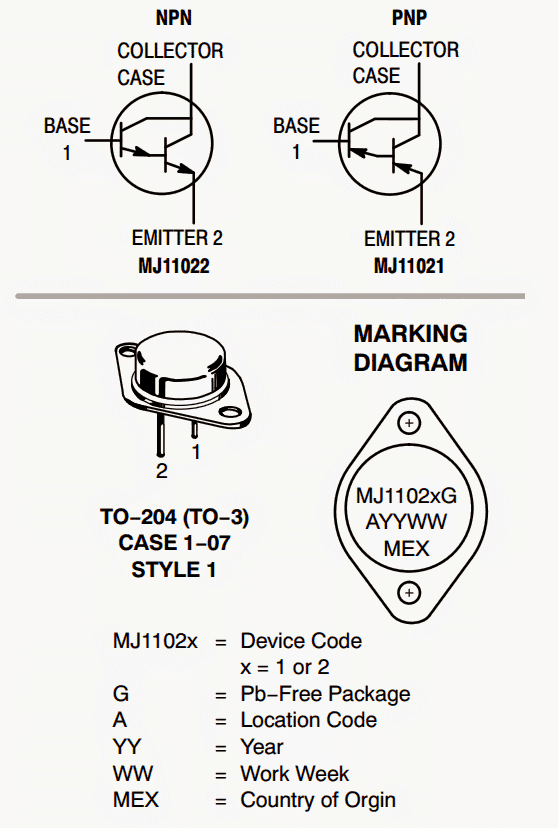

Yukarıdaki şekilde, üst invertör # 1'in ana inverteri oluştururken, alt invertör # 2'nin bağımlı olduğu birkaç özdeş aşama görebiliriz.

İnvertör # 3 ve invertör # 4 şeklindeki daha fazla aşamanın, bu invertörleri kendi bağımsız optokuplör aşamalarıyla entegre ederek aynı şekilde kuruluma eklenmesi beklenir, ancak opamp aşamasının tekrarlanması gerekmez.

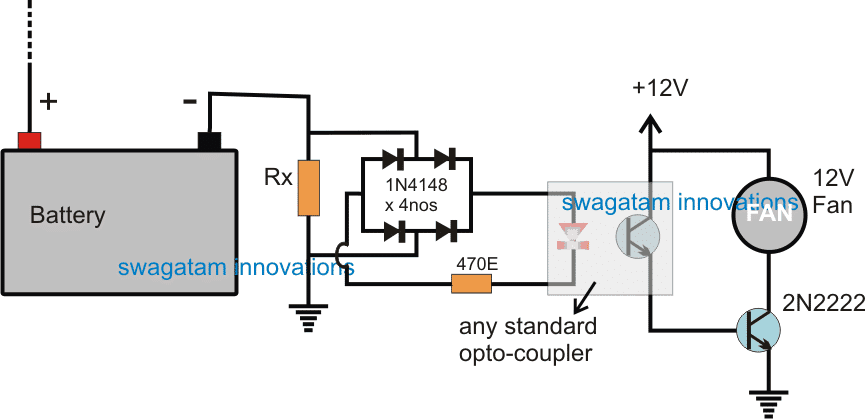

Tasarım öncelikle bir IC 555 tabanlı osilatör ve bir IC 4013 flip flop devresinden oluşur. IC 555, IC 4013'ün saat girişine beslenen 100 Hz veya 120 Hz hızında saat frekansları üretecek şekilde tasarlanmıştır, daha sonra bunu, çıkışlarını dönüşümlü olarak pim # 1 boyunca mantıksal olarak yüksek olacak şekilde çevirerek gerekli 50 Hz veya 60 Hz değerine dönüştürür. ve 2. pim.

Bu alternatif çıkışlar daha sonra güç cihazlarını ve transformatörü amaçlanan 220V veya 120V AC'yi üretmek için etkinleştirmek için kullanılır.

Şimdi, daha önce tartışıldığı gibi, buradaki en önemli konu, frekans, faz ve PWM açısından tam olarak senkronize çalışabilmeleri için iki invertörü senkronize etmektir.

Başlangıçta ilgili tüm modüller (istiflenebilir invertör devreleri), davranışları birbiriyle mükemmel şekilde eşit olacak şekilde, tam olarak aynı bileşenlerle ayrı ayrı ayarlanır.

Bununla birlikte, tam olarak eşleştirilmiş özniteliklerle bile, eviricilerin, benzersiz bir şekilde bağlanmadıkça mükemmel bir şekilde senkronize olarak çalışması beklenemez.

Bu aslında, yukarıdaki tasarımda belirtildiği gibi bir opamp / optocoupler aşaması aracılığıyla 'bağımlı' invertörleri entegre ederek yapılır.

Başlangıçta, ana invertör # 1 AÇIK konuma getirilir, bu da opamp 741 aşamasının güç almasına ve çıkış voltajının frekans ve faz takibini başlatmasına izin verir.

Bu başlatıldığında, ana hat hattına güç eklemek için sonraki eviricilerin tümü AÇIK konuma getirilir.

Görülebileceği gibi, opamp çıkışı, bağımlı invertörleri ana invertörün frekansını ve faz açısını takip etmeye zorlayan bir opto kuplör aracılığıyla tüm bağımlı inverterlerin zamanlama kapasitörüne bağlanır.

Bununla birlikte, burada ilginç olan, opampın anlık faz ve frekans bilgisi ile mandallama faktörüdür.

Bu, tüm invertörlerin ana invertörden belirtilen frekans ve fazda teslim ettiği ve çalıştığı için gerçekleşir; bu, ana invertör dahil invertörlerden herhangi birinin arızalanması durumunda opamp, anlık frekansı hızlı bir şekilde izleyebilir ve enjekte edebilir. faz bilgisi ve mevcut invertörleri bu spesifikasyonlarla çalışmaya zorlar ve invertör, geçişleri kesintisiz ve kendi kendini optimize etmek için opamp aşamasına geri bildirimleri sürdürebilir.

Bu nedenle, umarız opamp aşaması, önerilen tüm istiflenebilir invertörleri mevcut şebeke spesifikasyonunun CANLI bir şekilde izlenmesi yoluyla mükemmel şekilde senkronize halde tutmanın ilk zorluğunun üstesinden gelir.

Makalenin sonraki bölümünde şunları öğreneceğiz senkronize PWM sinüs dalgası aşaması , yukarıda tartışılan tasarımın bir sonraki önemli özelliği budur.

Bu makalenin yukarıdaki bölümünde, tasarımın senkronizasyon detaylarını açıklayan 4kva senkronize istiflenebilir invertör devresinin ana bölümünü öğrendik. Bu makalede, tasarımın nasıl bir sinüs dalgası eşdeğeri yapılacağını ve ayrıca ilgili invertörler arasında PWM'lerin doğru senkronizasyonunun nasıl sağlanacağını inceliyoruz.

İnvertörler arasında Sinüs PWM Senkronizasyonu

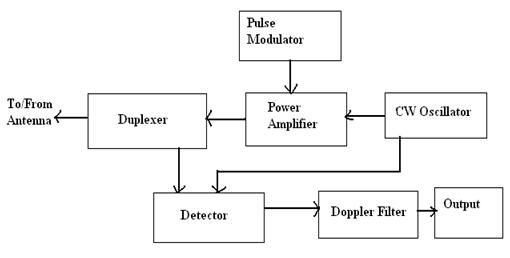

Aşağıdaki şekilde gösterildiği gibi, bir IC 555 ve IC 4060 kullanılarak basit bir RMS uyumlu PWM eşdeğeri sinüs dalgası dalga biçimi üreteci yapılabilir.

Bu tasarım daha sonra eviricilerin çıkışlarında ve bağlı ana hat boyunca sinüs dalgasına eşdeğer bir dalga formu üretmesini sağlamak için kullanılabilir.

Bu PWM işlemcilerin her biri, istiflenebilir invertör modüllerinin her biri için ayrı ayrı gerekli olacaktır.

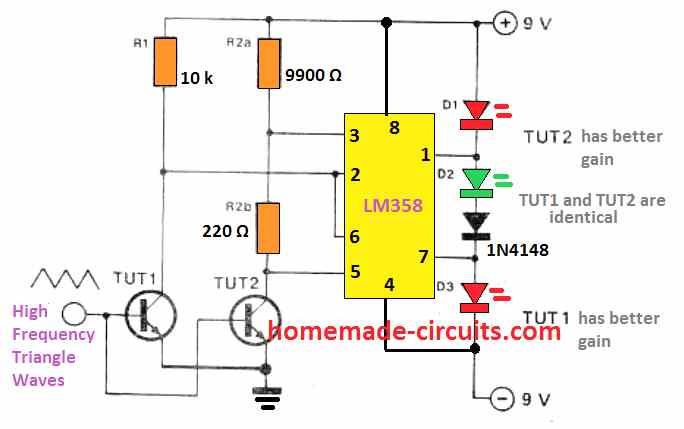

GÜNCELLEME: Görünüşe göre tek bir PWM işlemcisi, tüm transistör tabanlarını kesmek için ortak olarak kullanılabilir, ancak her MJ3001 tabanı, belirli bir BC547 toplayıcıya ayrı bir 1N4148 diyot aracılığıyla bağlanır. Bu, tasarımı büyük ölçüde basitleştirir.

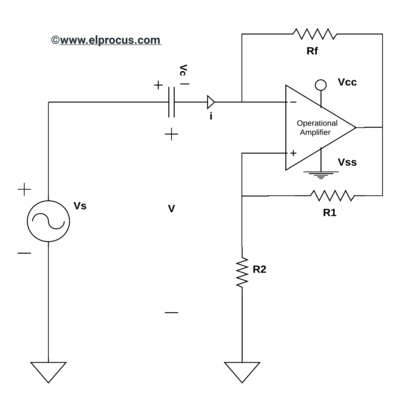

Yukarıdaki PWM geneartor devresinde yer alan farklı aşamalar, aşağıdaki noktanın yardımıyla anlaşılabilir:

IC 555'i PWM Üreteci olarak kullanma

IC 555, temel PWM jeneratör devresi olarak yapılandırılmıştır. İstenen RMS'de ayarlanabilir bir PWM eşdeğer darbeleri üretebilmek için IC, piminde 7 hızlı üçgen dalgalara ve piminde 5 çıkış pini # 3'teki PWM seviyesini belirleyen bir referans potansiyeline ihtiyaç duyar.

IC 4060'ı Üçgen Dalga Üreteci olarak kullanma

Üçgen dalgaları oluşturmak için IC 555, IC 4060 osilatör çipinden elde edilen 2 numaralı pininde kare dalgalara ihtiyaç duyar.

IC 4060, PWM'nin frekansını veya sadece AC yarı çevrimlerinin her birindeki 'sütunların' sayısını belirler.

IC 4060 esas olarak invertör çıkışından gelen örnek düşük frekans içeriğini, pim # 7'den nispeten yüksek bir frekansa çarpmak için kullanılır. Örnek frekansı temel olarak PWM doğramasının tüm invetrer modüller için eşit ve senkronize olmasını sağlar. IC 4060'ın dahil edilmesinin ana nedeni budur, aksi takdirde başka bir IC 555 işi kolayca yapabilirdi.

IC 555'in 5 numaralı pimindeki referans potansiyel, devrenin en solunda gösterilen bir opamp voltaj takipçisinden elde edilir.

Adından da anlaşılacağı gibi, bu opamp, pim # 3'te görünen pim # 6'da tam olarak aynı büyüklükte voltaj sağlar ... ancak pim # 3'ün pim # 6 kopyası güzel bir şekilde tamponlanmıştır ve bu nedenle ondan daha zengindir. pin3 kalitesi ve bu aşamayı tasarıma dahil etmenin tam nedeni budur.

Bu IC'nin pin3'ünde ilişkili 10 k ön ayar, nihayetinde IC 555 çıkış PWM'lerini istenen RMS seviyesine ince ayarlayan RMS seviyesini ayarlamak için kullanılır.

Bu RMS daha sonra güç cihazlarının tabanlarına, onları belirtilen PWM RMS seviyelerinde çalışmaya zorlamak için uygulanır, bu da AC çıkışının doğru bir RMS seviyesi aracılığıyla saf sinüs dalgası benzeri bir öznitelik elde etmesine neden olur. Bu, tüm transformatörlerin çıkış sargısı boyunca bir LC filtresi kullanılarak daha da geliştirilebilir.

Bu 4kva istiflenebilir senkronize invertör devresinin sonraki ve son kısmı, invertörlerin değişen yük anahtarlamasına uygun olarak çıkış gücü ana hattı boyunca doğru miktarda watt vermesini ve bunu korumasını sağlamak için otomatik yük düzeltme özelliğini ayrıntılarıyla açıklar.

Şimdiye kadar, frekans, faz ve PWM'nin invertörler arasında senkronizasyonunu içeren, önerilen senkronize 4kva istiflenebilir invertör devresi için iki ana gereksinimi ele aldık, böylece invertörlerden herhangi birinin arızalanmasının yukarıdaki parametreler açısından geri kalanı üzerinde hiçbir etkisi olmadı .

Otomatik Yük Düzeltme Aşaması

Bu yazıda, çıkış ana hattı boyunca değişen yük koşullarına yanıt olarak eviricilerin sırayla AÇIK veya KAPALI konuma getirilmesini sağlayabilecek otomatik yük düzeltme özelliğini bulmaya çalışacağız.

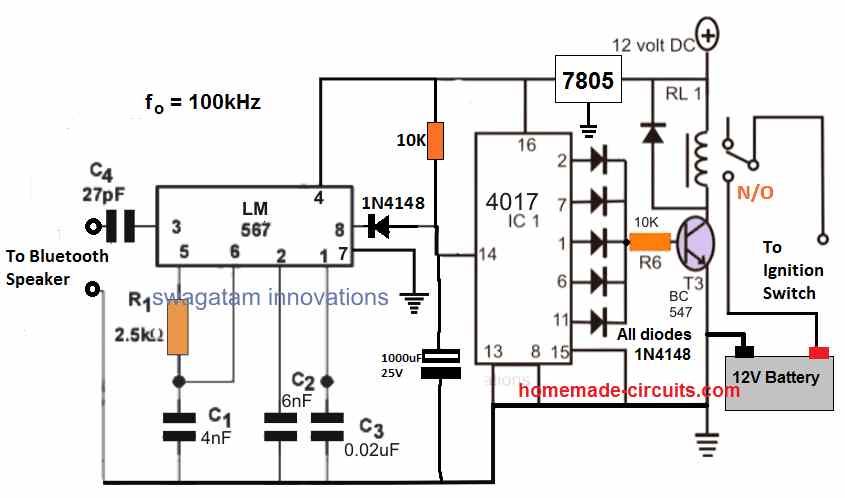

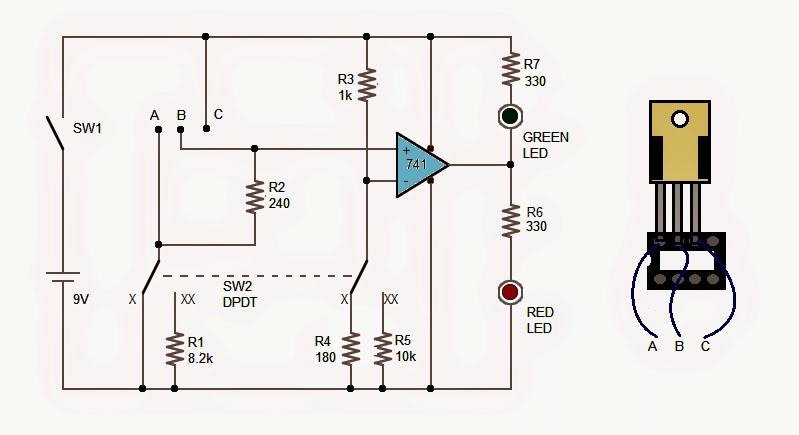

LM324 IC kullanan basit bir dörtlü karşılaştırıcı, aşağıdaki şemada gösterildiği gibi bir otomatik sıralı yük düzeltmesi uygulamak için kullanılabilir:

Yukarıdaki şekilde, IC LM324'ten dört ayrı karşılaştırıcı olarak yapılandırılmış dört opamp görebiliyoruz, ters çevirme girişlerinin tümü sabit bir zener voltajı ile referanslanırken, ters çevirmeyen girişleri ayrı ön ayarlarla donatılmıştır.

İlgili ön ayarlar, basitçe, opampların, şebeke voltajı amaçlanan eşiğin üzerine çıktığı anda bir ardışık olarak yüksek çıkışlar üreteceği şekilde ayarlanır ..... ve bunun tersi de geçerlidir.

Bu olduğunda, ilgili transistörler opamp aktivasyonuna göre değişir.

İlgili BJT'lerin toplayıcıları, PWM denetleyici aşamasında kullanılan voltaj izleyici opamp IC 741'in 3 numaralı pimine bağlanır ve bu, opamp çıkışını düşük veya sıfıra zorlar, bu da sıfır voltajın görünmesine neden olur. PWM IC 555'in 5. piminde (Bölüm 2'de tartışıldığı gibi).

IC 555'in 5 numaralı pini bu sıfır mantığıyla uygulandığında, PWM'leri en dar veya minimum değerde olmaya zorlar ve bu da söz konusu invertörün çıkışının neredeyse kapanmasına neden olur.

Yukarıdaki eylemler, çıktıyı daha önceki bir normal duruma stabilize etme girişiminde bulunur, bu da PWM'yi daha geniş olmaya zorlar ve bu savaş çekişmesi veya opampların sabit bir şekilde değiştirilmesi, çıktıyı mümkün olduğu kadar istikrarlı bir şekilde tutar. ekli yüklerin varyasyonları.

Önerilen 4kva istiflenebilir invertör devresinde uygulanan bu otomatik yük düzeltmesi ile tasarımı, makalenin 1. Bölümünde kullanıcı tarafından talep edilen tüm özelliklerle neredeyse eksiksiz hale getirir.

Önceki: Bu SleepWalk Uyarısını Yapın - Kendinizi Uyurgezerlik Tehlikelerinden Koruyun Sonraki: IC 555 Pinouts, Astable, Monostable, Bistable Devreler Keşfedilen Formüller ile