alan etkili transistör (FET) bir elektronik cihazdır. Elektrik alanı akımın akışını düzenlemek için kullanılır. Bunu uygulamak için, cihazın geçit ve kaynak terminalleri boyunca, boşaltma ve kaynak terminalleri arasındaki iletkenliği değiştiren, bu terminaller boyunca kontrollü bir akımın akmasına neden olan bir potansiyel fark uygulanır.

FET'ler çağrılır tek kutuplu transistörler çünkü bunlar tek taşıyıcılı tip cihazlar olarak çalışmak üzere tasarlanmıştır. Farklı alan etkili transistör türlerini bulabilirsiniz.

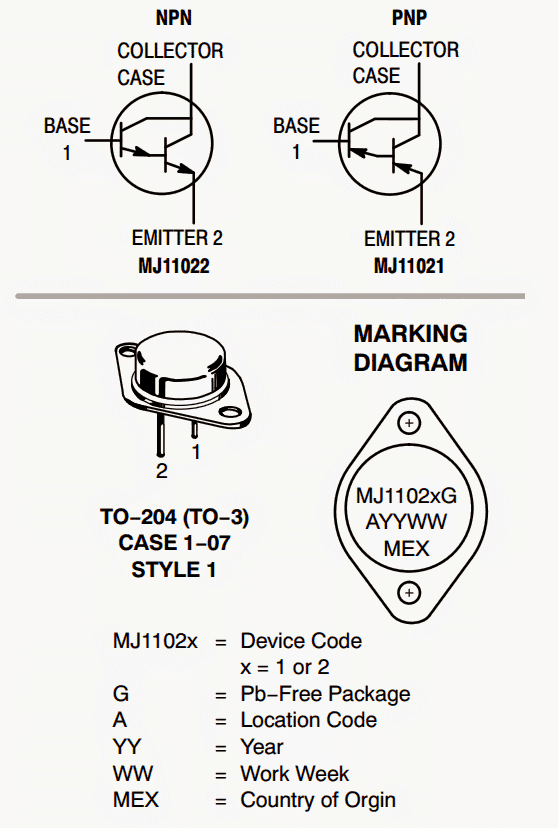

Sembol

N-kanal ve p-kanal JFET'ler için grafik semboller aşağıdaki şekillerde görselleştirilebilir.

N-kanallı aygıt için içeri doğru işaret eden ok işaretlerinin, hangi yöne doğru hareket ettiğimi açıkça fark edebilirsiniz.G(kapı akımı), p-n bağlantısı ileri eğilimli olduğunda akması gerekiyordu.

Bir p-kanal cihazı durumunda, ok sembolünün yönündeki fark dışında koşullar aynıdır.

FET ve BJT arasındaki fark

Alan etkili transistör (FET), BJT transistörünkileri büyük ölçüde tamamlayan çok çeşitli devre uygulamaları için tasarlanmış üç terminalli bir cihazdır.

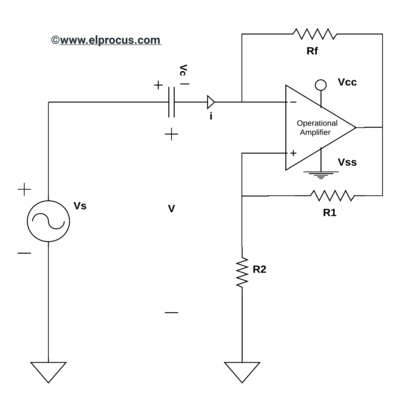

BJT'ler ve JFET'ler arasında önemli farklılıklar bulacak olsanız da, aslında aşağıdaki tartışmalarda bahsedilecek olan birkaç eşleşen özellik vardır. Bu cihazlar arasındaki temel ayrım, BJT'nin Şekil 5.1a'da gösterildiği gibi akım kontrollü bir cihaz olması, JFET transistörü ise Şekil 5.1b'de gösterildiği gibi voltaj kontrollü bir cihaz olmasıdır.

Basitçe söylemek gerekirse, mevcut benCŞekil 5.1a, I seviyesinin anlık bir fonksiyonudur.B. FET için akım I, V geriliminin bir fonksiyonudur.GSŞekil 5.1b'de gösterildiği gibi giriş devresine verilir.

Her iki durumda da çıkış devresinin akımı, giriş devresinin bir parametresi tarafından yönetilecektir. Bir durumda bir akım seviyesi ve diğerinde uygulanan bir voltaj.

Bipolar transistörler için npn ve pnp gibi, n-kanallı ve p-kanallı alan etkili transistörleri bulacaksınız. Ancak, BJT transistörünün iki kutuplu bir cihaz olduğunu unutmamalısınız, ön ek iki kutupludur ki bu, iletim seviyesinin iki yük taşıyıcısının, elektronların ve deliklerin bir fonksiyonu olduğunu gösterir.

Öte yandan FET, bir tek kutuplu cihaz bu sadece elektron (n-kanal) veya delik (p-kanal) iletimine bağlıdır.

'Alan etkisi' ifadesi şu şekilde açıklanabilir: Hepimiz kalıcı bir mıknatısın herhangi bir fiziksel temas olmaksızın metal talaşları mıknatısa doğru çekme gücünün farkındayız. FET içinde oldukça benzer bir şekilde, kontrol eden ve kontrol edilen büyüklükler arasında herhangi bir doğrudan temas olmaksızın çıkış devresinin iletim yolunu etkileyen mevcut yükler tarafından bir elektrik alanı yaratılır. Muhtemelen FET'in en önemli özelliklerinden biri yüksek giriş empedansıdır.

Doğrusal ac amplifikatör modelleri geliştirirken son derece önemli bir özellik olan BJT konfigürasyonlarının normal giriş direnci aralıklarını önemli ölçüde aşar.

Bununla birlikte, BJT, giriş sinyalindeki değişikliklere karşı daha büyük bir hassasiyet taşır. Yani, çıkış akımındaki değişiklik, giriş voltajlarındaki aynı miktarda değişiklik için BJT'ler için FET'lerden çok daha fazladır.

Bu nedenle, BJT amplifikatörleri için standart ac voltaj kazançları, FET'lere kıyasla çok daha yüksek olabilir.

Genel olarak konuşursak, FET'ler termal olarak BJT'lerden önemli ölçüde daha dayanıklıdır ve ayrıca BJT'lere kıyasla yapı olarak genellikle daha küçük boyuttadır, bu da onları entegre devre (IC)cips.

Öte yandan, bazı FET'lerin yapısal özellikleri, fiziksel temaslara BJT'lerden daha hassas olmalarına izin verebilir.

Daha Fazla BJT / JFET İlişkisi

- BJT V içinBE= 0,7 V, konfigürasyonunun analizine başlamak için önemli faktördür.

- Benzer şekilde, parametre IG= 0 A genellikle bir JFET devresinin analizi için düşünülen ilk şeydir.

- BJT yapılandırması için, benBgenellikle belirlenmesi gereken ilk faktördür.

- Benzer şekilde, JFET için tipik olarak VGS.

Bu yazıda JFET'lere veya bağlantı alanı etkili transistörlere odaklanacağız, sonraki makalede metal oksit yarı iletken alan etkili transistör veya MOS-FET hakkında konuşacağız.

JFET'LERİN YAPISI VE ÖZELLİKLERİ

Erken öğrendiğimiz gibi, bir JFET'in 3 ipucu var. Bunlardan biri, diğer ikisi arasındaki akım akışını kontrol eder.

Tıpkı BJT'ler gibi, JFET'lerde de n-kanallı cihaz, p-kanallı emsallerinden daha belirgin bir şekilde kullanılmaktadır, çünkü n cihaz, p-cihazına kıyasla daha verimli ve kullanıcı dostu olma eğilimindedir.

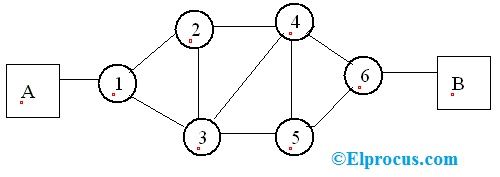

Aşağıdaki şekilde bir n-kanal JFET'in temel yapısını veya yapısını görebiliriz. N-tipi bileşimin, p-tipi katmanlar boyunca ana kanalı oluşturduğunu görebiliriz.

N-tipi kanalın üst kısmı, drenaj (D) adı verilen bir terminal ile Ohmik bir temas yoluyla birleştirilirken, aynı kanalın alt kısmı da bir Ohmik kontak yoluyla kaynak (S) adı verilen başka bir terminal ile bağlanır.

P-tipi malzemelerin çifti, kapı (G) olarak anılan terminale birbirine bağlıdır. Esasen, boşaltma ve kaynak terminallerinin n-tipi kanalın uçlarına birleştirildiğini buluyoruz. Kapı terminali, bir çift p-kanallı malzemeye birleştirilir.

Bir jfet boyunca voltaj uygulanmadığında, iki p-n bağlantısı herhangi bir önyargı koşulu içermez. Bu durumda, yukarıdaki şekilde gösterildiği gibi her bir bağlantı noktasında bir tükenme bölgesi vardır ve bu, hiçbir önyargı altında olmayan bir diyot p-n bölgesine oldukça benzer.

Su Analojisi

Bir JFET'in çalışma ve kontrol operasyonları aşağıdaki su benzetmesiyle anlaşılabilir.

Burada su basıncı, drenajdan kaynağa doğru uygulanan voltaj büyüklüğü ile karşılaştırılabilir.

Suyun akışı, elektronların akışıyla karşılaştırılabilir. Musluğun ağzı JFET'in kaynak terminalini taklit ederken, musluğun suyun zorlandığı üst kısmı JFET'in Boşaltımını gösterir.

Musluk düğmesi, JFET'in Kapısı gibi davranır. Tıpkı musluk düğmesinin ağız açıklığındaki su akışını kontrol etmesi gibi, bir giriş potansiyeli yardımıyla elektronların akışını (yük) drenajdan kaynağa kontrol eder.

JFET yapısından, drenaj ve kaynak terminallerin n-kanalının zıt uçlarında olduğunu görebiliriz ve terim elektron akışına dayandığından şunu yazabiliriz:

VGS= 0 V, VDSBazı Olumlu Değerler

Şekil 5.4'te pozitif bir voltaj V görebilirizDSn-kanalı boyunca uygulanır. Kapı terminali, bir V koşulu oluşturmak için doğrudan kaynağa bağlanırGS= 0V. Bu, geçidin ve kaynak terminallerin aynı potansiyelde olmasını sağlar ve her bir p-malzemesinin bir alt uç tükenme bölgesi ile sonuçlanır, aynen yukarıdaki ilk diyagramda önyargı olmayan bir koşulda gördüğümüz gibi.

Voltaj V olduğu andaDD(= VDS) uygulandığında, elektronlar Şekil 5.4'te gösterildiği gibi geleneksel akım ID akışını oluşturarak boşaltma terminaline doğru çekilir.

Yükün akış yönü, drenaj ve kaynak akımının büyüklük olarak eşit olduğunu ortaya koymaktadır (ID= IS). Şekil 5.4'te gösterilen koşullara göre, yükün akışı oldukça sınırsız görünüyor ve yalnızca drenaj ile kaynak arasındaki n-kanalının direncinden etkileniyor.

Her iki p-tipi malzemenin üst kısmı etrafında tükenme bölgesinin daha büyük olduğunu gözlemleyebilirsiniz. Bölgenin boyutundaki bu farklılık ideal olarak Şekil 5.5 ile açıklanmaktadır. N-kanalında tekdüze bir direncin olduğunu hayal edelim, bu Şekil 5.5'te belirtilen bölümlere ayrılabilir.

Akım benDaynı şekilde gösterildiği gibi kanal üzerinden voltaj aralıkları oluşturabilir. Sonuç olarak, p-tipi malzemenin üst bölgesi, yaklaşık 1.5 V'lik bir seviye ile ters yönde önyargılı olacaktır, alt bölge sadece 0.5 V ile ters yönlü olacaktır.

P-n bağlantısının tüm kanal boyunca ters yönlü olduğu nokta, aynı şekilde gösterildiği gibi sıfır amperli bir kapı akımına yol açar. Bene götüren bu özellikG= 0 A, JFET'in önemli bir özelliğidir.

V olarakDSpotansiyel 0'dan birkaç volta yükseltilir, akım Ohm yasasına ve I'in grafiğine göre artar.Dsatır 5DSŞekil 5.6'da kanıtlandığı gibi görünebilir.

Çizimin karşılaştırmalı düzlüğü, V'nin düşük değerli bölgeleri içinDSdirenç temelde tek tiptir. V olarakDSŞekil 5.6'da VP olarak bilinen bir seviyeye yükselir ve yaklaşır, tükenme bölgeleri Şekil 5.4'te verildiği gibi genişler.

Bu, kanal genişliğinde belirgin bir düşüşe neden olur. Azalan iletim yolu, Şekil 5.6'daki eğriye yol açan direnç artışına yol açar.

Eğri ne kadar yatay olursa, direnç o kadar yüksek olur, bu da direncin yatay bölgede “sonsuz” ohm'a doğru gittiğini gösterir. Ne zaman VDSŞekil 5.7'de gösterildiği gibi iki tükenme bölgesinin 'temas edebileceği' göründüğü ölçüde artar, sıkıştırma olarak bilinen bir duruma yol açar.

V'ninDSgeliştirir bu duruma denir çimdiklemek gerilim ve V ile sembolize edilirPŞekil 5.6'da gösterildiği gibi. Genel olarak, pinch-off kelimesi yanıltıcıdır çünkü mevcut ID'sıkışmış' ve 0 A'ya düşüyor. Şekil 5.6'da kanıtlandığı gibi, bu durumda bu pek belirgin görünmüyor. benDI olarak karakterize edilen bir doygunluk seviyesini korurDSSŞekil 5.6.

Gerçek şu ki, oldukça yüksek konsantrasyonlu bir akımla çok küçük bir kanal var olmaya devam ediyor.

Kimliğin düşmediği nokta çimdiklemek ve Şekil 5.6'da gösterildiği gibi doygunluk seviyesini korur, aşağıdaki kanıtla doğrulanır:

Boşaltma akımı olmadığından, p-n bağlantısı boyunca değişen ters önyargı miktarlarını belirlemek için n-kanal malzemesi aracılığıyla farklı potansiyel seviyeleri olasılığını ortadan kaldırır. Sonuç, tetiklenen tükenme bölgesi dağılımının kaybıdır. çimdiklemek ile başlamak için.

V'yi artırdıkçaDSV'nin üstündePiki tükenme bölgesinin birbiriyle karşılaşacağı yakın temas bölgesinin kanal boyunca uzunluğu artar. Ancak kimlik seviyesi esasen değişmeden kalmaya devam ediyor.

Böylece V anıDSV'den yüksektirpJFET, akım kaynağının özelliklerini edinir.

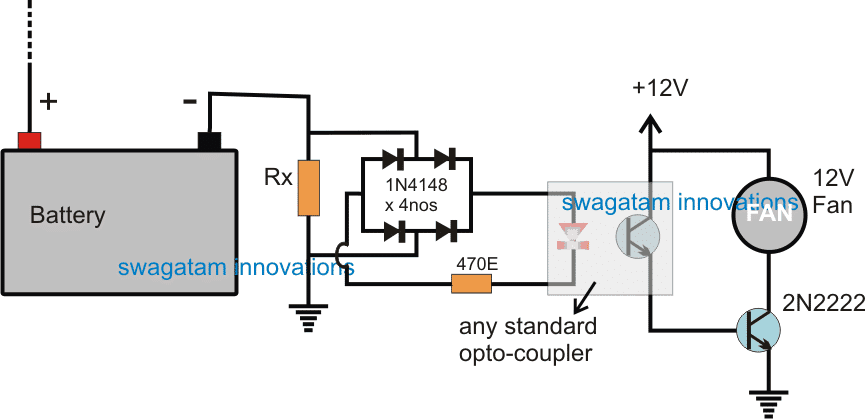

Şekil 5.8'de kanıtlandığı gibi, bir JFET'teki akım I'de belirlenirD= IDSS, ancak voltaj VDSBağlı yük tarafından VP'den daha yüksek oluşturulur.

IDSS notasyonunun seçimi, kapıdan kaynağa kısa devreli bir bağlantıya sahip Kaynağa Boşaltma akımı olduğu gerçeğine dayanmaktadır.

Daha fazla araştırma bize şu değerlendirmeyi verir:

benDSSbir JFET için en yüksek boşaltma akımıdır ve V koşulları tarafından belirlenirGS= 0 V ve VDS> | VP |.

Şekil 5.6 V'ye dikkat edin.GSeğrinin tam uzatılması için 0V'dir. Aşağıdaki bölümlerde, Şekil 5.6 özniteliklerinin V seviyesi olarak nasıl etkilendiğini öğreneceğiz.GSÇeşitlidir.

VGS <0V

Kapı ve kaynak boyunca uygulanan dalgalanma, JFET işlemlerinin kontrolünden sorumlu olan VGS olarak belirtilir.

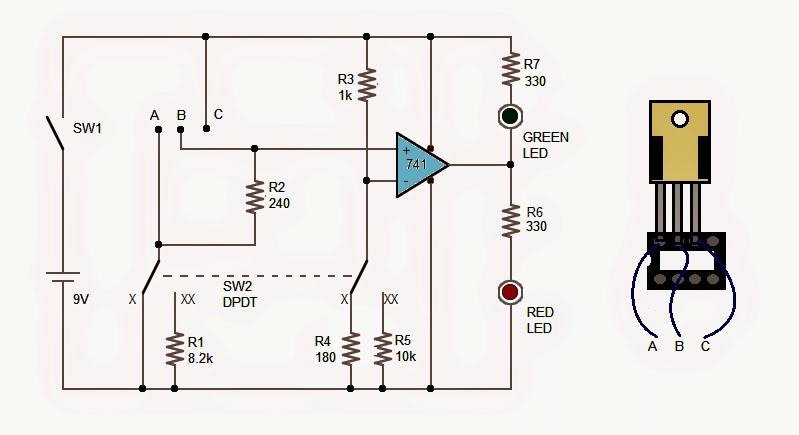

Bir BJT örneğini alırsak, tıpkı I'in eğrileri gibiCvs VBUI'in çeşitli seviyeleri için belirlenirBbenzer şekilde I eğrileriDvs VDSçeşitli V seviyeleri içinGSJFET muadili için oluşturulabilir.

Bunun için geçit terminali, kaynak potansiyel seviyesinin altında devam eden bir düşük potansiyele ayarlanmıştır.

Aşağıdaki Şekil 5.9'a atıfta bulunarak, azaltılmış bir V için kapı / kaynak terminalleri boyunca bir -1V uygulanır.DSseviyesi.

Negatif potansiyel önyargının amacı VGSV'nin durumuna benzeyen tükenme bölgeleri geliştirmektir.GS= 0, ancak önemli ölçüde azaltılmış V'deDS.

Bu, kapının daha düşük V seviyelerine sahip bir doyma noktasına ulaşmasına neden olur.DSŞekil 5.10'da gösterildiği gibi (VGS= -1V).

I için karşılık gelen doygunluk seviyesiDazalmış olarak bulunabilir ve aslında V olarak azalmaya devam ederGSdaha olumsuz yapılır.

Şekil 5.10'da kıstırma geriliminin V olarak parabolik bir şekilde düşmeye devam ettiğini açıkça görebilirsiniz.GSgittikçe daha fazla olumsuz oluyor.

Son olarak, VGS= -Vp, sonunda 0 mA olan bir doygunluk seviyesi oluşturmak için yeterince negatif olur. Bu seviyede, JFET tamamen 'KAPALI'dır.

V seviyesiGSki benD0 mA'ya ulaşmak V ile karakterizedirGS= VP, burada VPn kanallı cihazlar için negatif voltaj ve p kanallı JFET'ler için pozitif voltajdır.

Genellikle, JFET veri sayfalarının çoğunun çimdiklemek V olarak belirtilen voltajGS (kapalı)V yerineP.

Yukarıdaki şekilde kıstırma lokusunun sağ tarafındaki alan, distorsiyonsuz sinyal elde etmek için doğrusal amplifikatörlerde geleneksel olarak kullanılan yerdir. Bu bölge genellikle sabit akım, doygunluk veya doğrusal amplifikasyon bölgesi.

Voltaj kontrollü Direnç

Aynı şekilde kıstırma lokusunun sol tarafında bulunan alana, omik bölge veya voltaj kontrollü direnç bölgesi.

Bu bölgede cihaz aslında, uygulanan kapı / kaynak potansiyeli aracılığıyla kontrol edilen direnci ile değişken bir direnç olarak (örneğin otomatik kazanç kontrol uygulamasında) çalıştırılabilir.

Her bir eğrinin eğiminin, aynı zamanda JFET'in V için boşaltma / kaynak direncini de ifade ettiğini görebilirsiniz.DS

VGS'yi negatif potansiyel ile yükselttikçe, her eğrinin eğimi gittikçe daha yatay hale gelir ve orantılı olarak artan direnç seviyeleri sergiler.

Aşağıdaki denklem aracılığıyla, VGS voltajına göre direnç seviyesine iyi bir başlangıç yaklaşımı elde edebiliyoruz.

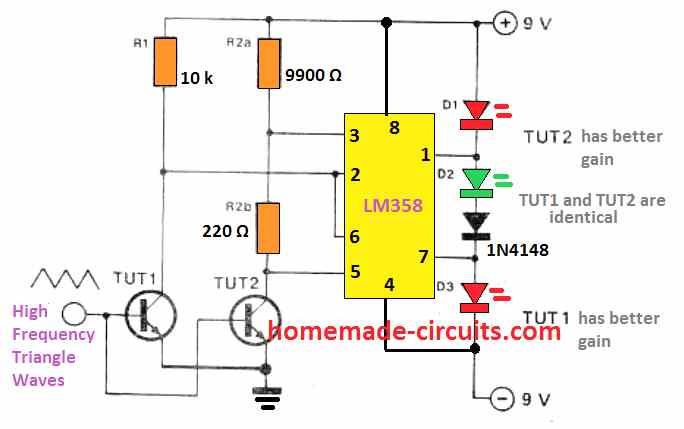

p-Kanal JFET Çalışması

Bir p-kanal JFET'in dahili düzeni ve yapısı, aşağıda gösterildiği gibi, p ve n tipi malzeme bölgelerinin tersine çevrilmesi dışında n kanallı muadili ile tam olarak aynıdır:

Akım akışının yönleri, gerilim VGS ve VDS'nin gerçek polariteleri ile birlikte tersine çevrilmiş olarak da görülebilir. Bir p-kanal JFET durumunda, kanal, geçit / kaynak boyunca artan pozitif potansiyele yanıt olarak kısıtlanacaktır.

V için çift alt simgeli gösterimDSV için negatif gerilime neden olurDSŞekil 5.12'nin özelliklerinde gösterildiği gibi. Burada bulabilirsinDSS6 mA'da, V'de bir kısma gerilimiGS= + 6V.

V için eksi işaretinin varlığından dolayı lütfen şaşırmayın.DS. Basitçe, kaynağın drenajdan daha yüksek bir potansiyel taşıdığını gösterir.

Gördüğünüz gibi yüksek V için eğrilerDSseviyeler aniden sınırsız görünen değerlere yükselir. Dikey olan belirtilen yükselme, bir arıza durumunu sembolize eder, bu, kanal cihazından geçen akımın, bu zaman noktasında tamamen harici devre tarafından kontrol edildiği anlamına gelir.

Bu, n kanallı cihaz için Şekil 5.10'da açık olmasa da, yeterince yüksek voltaj altında bir olasılık olabilir.

Bu bölge, eğer VDS (maks.)cihazın veri sayfasından not edilir ve cihaz, gerçek VDSherhangi bir V için bu belirtilen değerden daha düşükGS.

Bir çift: 5 En İyi 40 Watt Amplifikatör Devresi Keşfedildi Sonraki: 2N3055 Veri Sayfası, Pinout, Uygulama Devreleri